Kodėl verta naudoti Xilinx FPGA XC3S500E-4FTG256I?

Jei esate elektronikos inžinerijos dizaineris, galbūt žinote lustą XC3S500E-4FTG256I .

Šis lauke programuojamas vartų masyvas (FPGA) plačiai naudojamas įvairiose srityse, nuo buitinės elektronikos iki pramonės valdymo, aviacijos, karinės ir kitose srityse.

FPGA yra puslaidininkinis įrenginys, sudarytas iš konfigūruojamų loginių blokų (CLB), sujungtų programuojamomis jungtimis, matricos. Vartotojas nustato šiuos tarpusavio ryšius programuodamas SRAM. CLB gali būti paprastas (IR, ARBA vartai ir tt) arba sudėtingas (RAM blokas). FPGA leidžia pakeisti dizainą net po to, kai įrenginys yra lituojamas į PCB.

Šiame straipsnyje sužinosite apie kai kuriuos „Xilinx“ XC3S500E-4FTG256I pagrindus, taip pat sužinosite, kaip profesionaliai jį naudoti ir jo funkcijas.

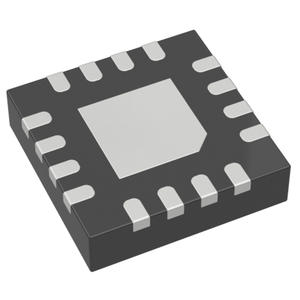

Kas yra XC3S500E-4FTG256I?

XC3S500E-4FTG256I priklauso Spartan-3E FPGA serijai, kurią sukūrė Xilinx.

Spartan-3E šeima siūlo ekonomišką FPGA sprendimą su mažu galios suvartojimu, dideliu našumu ir pažangiomis sistemos lygio funkcijomis.

Xilinx Zynq FPGA

XC3S500E-4FTG256I turi 500 000 sistemos vartų, 772 vartotojo įvesties / išvesties ir 36 blokų RAM.

Jis veikia maksimaliu 400 MHz dažniu, o šerdies įtampos diapazonas yra nuo 1,14 V iki 1,26 V.

XC3S500E-4FTG256I dažniausiai naudojamas aviacijos ir gynybos, automobilių, transliacijų, vartotojų, didelio našumo skaičiavimo, pramonės, medicinos ir mokslo, bandymų ir matavimų srityse.

Prašyti originalaus ir naujo Xilinx XC3S500E-4FTG256I FGPA dabar

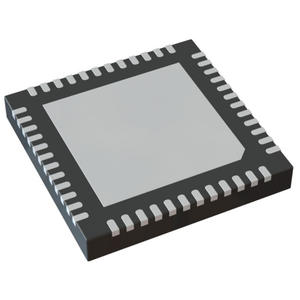

XC3S500E-4FTG256I savybės

• SelectIO signalizacija

– iki 633 įvesties/išvesties kaiščių

– aštuoniolika vieno galo signalo standartų

– aštuoni diferencinio signalo standartai, įskaitant LVDS ir RSDS

– dvigubo duomenų perdavimo spartos (DDR) palaikymas

• Loginiai ištekliai

– gausu loginių langelių su pamainų registro galimybe

– Platūs tankintuvai

– Greito žvilgsnio į priekį pernešimo logika

– specialūs 18 x 18 daugikliai

– JTAG logika suderinama su IEEE 1149.1/1532

• SelectRAM hierarchinė atmintis

– iki 1 728 Kbit viso bloko RAM

– iki 432 Kbit visos paskirstytos RAM

• Skaitmeninio laikrodžio tvarkyklė (keturi DCM)

– Laikrodžio iškrypimo pašalinimas

– Dažnio sintezė

– Didelės skiriamosios gebos fazių poslinkis

English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 繁體中文

繁體中文 Беларус

Беларус